AArch64¶

Instruction¶

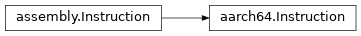

- class lief.assembly.aarch64.Instruction¶

Bases:

InstructionThis class represents an AArch64 instruction

- property opcode lief.assembly.aarch64.OPCODE¶

The instruction opcode as defined in LLVM

- property operands Iterator[lief.assembly.aarch64.Operand | None]¶

Iterator over the operands of the current instruction

Opcodes¶

See: lief.assembly.aarch64.OPCODE

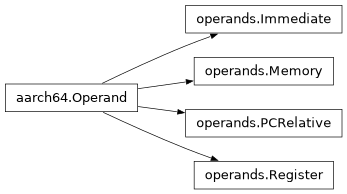

Operands¶

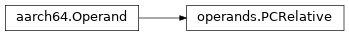

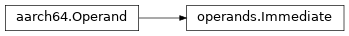

- class lief.assembly.aarch64.Operand¶

Bases:

objectThis class represents an operand for an AArch64 instruction

- property to_string str¶

Pretty representation of the operand

Immediate¶

Register¶

- class lief.assembly.aarch64.operands.Register¶

Bases:

OperandThis class represents a register operand.

mrs x0, TPIDR_EL0 | | +------+ +-------+ | | v v REG SYSREG- property value lief.assembly.aarch64.REG | lief.assembly.aarch64.SYSREG | None¶

The effective register as either: a

lief.assembly.aarch64.REGor alief.assembly.aarch64.SYSREG.

Memory¶

- class lief.assembly.aarch64.operands.Memory¶

Bases:

OperandThis class represents a memory operand.

ldr x0, [x1, x2, lsl #3] | | | +------------+ | +--------+ | | | v v v Base Reg Offset Shift- property base lief.assembly.aarch64.REG¶

The base register.

For

str x3, [x8, #8]it would returnx8.

- property offset lief.assembly.aarch64.REG | int | None¶

The addressing offset.

It can be either:

A register (e.g.

ldr x0, [x1, x3])An offset (e.g.

ldr x0, [x1, #8])

- property shift lief.assembly.aarch64.operands.Memory.shift_info_t¶

Shift information.

For instance, for

ldr x1, [x2, x3, lsl #3]it would return aLSLwith avalueset to3.

- class shift_info_t¶

Bases:

objectThis structure holds shift info (type + value)

- property type lief.assembly.aarch64.operands.Memory.SHIFT¶

- property value int¶

PCRelative¶